# Design and simulation of a 12-bit, 40 MSPS asynchronous SAR ADC for the readout of PMT signals $^*$

Jian-Feng Liu(刘建峰)<sup>1,2</sup> Lei Zhao(赵雷)<sup>1,2;1)</sup> Jia-Jun Qin(秦家军)<sup>1,2</sup> Yun-Fan Yang(杨云帆)<sup>1,2</sup> Li Yu(于莉)<sup>1,2</sup> Yu Liang(梁宇)<sup>1,2</sup> Shu-Bin Liu(刘树彬)<sup>1,2</sup> Qi An(安琪)<sup>1,2</sup>

Abstract: High precision and large dynamic range measurement are required in the readout systems for the Water Cherenkov Detector Array (WCDA) in the Large High Altitude Air Shower Observatory (LHAASO). This paper presents a prototype of a 12-bit 40 MSPS Analog-to-Digital Converter (ADC) Application Specific Integrated Circuit (ASIC) designed for the readout of the LHAASO WCDA. Combining this ADC and the front-end ASIC finished in our previous work, high precision charge measurement can be achieved based on the digital peak detection method. This ADC is implemented based on a power-efficient Successive Approximation Register (SAR) architecture, which incorporates key parts such as a Capacitive Digital-to-Analog Converter (CDAC), dynamic comparator and asynchronous SAR control logic. The simulation results indicate that the Effective Number Of Bits (ENOB) with a sampling rate of 40 MSPS is better than 10 bits in an input frequency range below 20 MHz, while its core power consumption is 6.6 mW per channel. The above results are good enough for the readout requirements of the WCDA.

Keywords: SAR ADC, asynchronous SAR logic, bootstrapped switch, dynamic comparator, LHAASO, WCDA

**PACS:** 84.30.-r, 07.05.Hd **DOI:** 10.1088/1674-1137/40/11/116103

#### 1 Introduction

The Large High Altitude Air Shower Observatory (LHAASO) project has been proposed for high energy gamma ray and cosmic ray detection [1–3]. One of the major components is the Water Cherenkov Detector Array (WCDA), which aims to survey the northern sky for very high energy (VHE) gamma ray sources. The WCDA is a ground-based Extensive Air Shower (EAS) detector, which adopts 3600 photomultiplier tubes (PMTs) to collect the Cherenkov light produced by the secondary particles of the EAS. To achieve wide energy spectrum observation with high energy resolution, the readout electronics for the WCDA are required to cover PMT signals in a range from single photoelectron (P.E.) to 4000 P.E. with precise time and charge measurement. A charge resolution of 30\% @ 1 P.E. and 3\% @ 4000 P.E. is required in the full dynamic range and the single-counting rate of a PMT can reach as high as 33-45 kHz [2].

For charge measurement, there are several methods applied in the readout electronics of high energy physics experiments, such as analog peak detection adopted in Refs. [4–7], digital peak detection adopted in Refs. [8–

11], the Time Over Threshold (TOT) principle adopted in Refs. [12–15], and waveform digitization based on a Switched Capacitor Array (SCA) adopted in Refs. [16–19]. The analog peak detection method has a relatively large dead time and the resolution of SCA-based waveform digitization is limited with high input signal frequency. In the readout electronics of the WCDA, we investigated the ASIC-based implementation of both TOT method and digital peak detection. The former can greatly simplify the structure of readout electronics while the latter has the advantages of better linearity and resolution. In this paper, we focus on the implementation of the latter. The charge measurement circuits are designed based on analog signal shaping, analog-to-digital conversion and digital peak detection logic.

In our previous work, a front-end ASIC [20] with the function of analog signal shaping has been designed. In this paper, we present the design and simulation of a prototype 12-bit 40 MSPS Successive Approximation Register (SAR) ADC to digitize the output signal of the front-end ASIC. The Effective Number Of Bits (ENOB) of the ADC aims to be better than 10 bits, which corresponds to an equivalent input noise of 0.69 mV for a 2

State Key Laboratory of Particle Detection and Electronics, University of Science and Technology of China, Hefei 230026, China,

Department of Modern Physics, University of Science and Technology of China, Hefei 230026, China

Received 5 January 2016, Revised 13 May 2016

<sup>\*</sup> Supported by Knowledge Innovation Program of the Chinese Academy of Sciences (KJCX2-YW-N27), CAS Center for Excellence in Particle Physics (CCEPP)

<sup>1)</sup> E-mail: zlei@ustc.edu.cn

<sup>©2016</sup> Chinese Physical Society and the Institute of High Energy Physics of the Chinese Academy of Sciences and the Institute of Modern Physics of the Chinese Academy of Sciences and IOP Publishing Ltd

$V_{\rm PP}$  full scale input range. In this condition, the charge resolution contributed by the ADC for 1 P.E. signal is better than 5%, which is good enough for overall resolution requirement (30\%@1 P.E.). The large number of readout channels demands low power consumption to release the pressure of the cooling system on high altitude mountains. Therefore, the SAR architecture [21–22] is adopted for its simplicity and power efficiency in deepsub-micron CMOS technology compared with pipelined architecture [8, 23]. The rest of this paper is organized as follows. Firstly, the overall architecture of the PMT readout electronics is presented in Section 2. Section 3 describes the ADC architecture. Then Section 4 presents the design and implementation of key circuit blocks of the ADC ASIC. Simulation results are presented in Section 5. Finally, the conclusions are given.

# 2 Architecture of PMT readout electronics

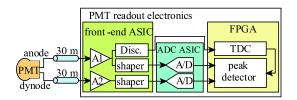

The overall architecture of the PMT readout electronics is presented in Fig. 1. Each PMT exports two signals from the anode and tenth dynode, respectively. Then the signals are sent to the front-end ASIC [20] via 30 m coaxial cables. This ASIC integrates two functions: one is leading edge discrimination and the other is shaping. The output of the discriminator is then digitized by the Time-to-Digital Converter (TDC) to achieve time measurement, which is implemented by the logic in the Field Programmable Gate Array (FPGA). The output waveform of the shaper is digitized by the ADC ASIC and then the output data of the ADC are sent to the peak detector logic in the FPGA to achieve charge measurement.

For charge measurement, we employ two readout channels to record the PMT signals from the anode and tenth dynode, respectively. The anode channel covers 1 to 100 P.E. and the tenth dynode channel covers 40 to 4000 P.E. Thus we can achieve 4000 dynamic range with a sufficient overlap. Each readout channel consists of pre-amplifier, shaper and ADC. Since the pre-amplifier and shaper were realized in the front-end ASIC [20], this paper focuses on the design of ADC ASIC prototype for the readout of PMT signal. The ADC prototype has four channels (corresponding to two PMT readout channels) and each ADC has a resolution of 12 bits, which is sufficiently to cover 100 dynamic range. Thanks to the amplification and shaping of the original PMT signal by the front-end ASIC [20], the demand for the sampling rate and ENOB of the ADC ASIC can be greatly decreased, which means that it consumes much less power than that used in real time waveform digitization. In summary, an ADC with medium speed (40 MSPS) and mediumto-high resolution (12 bit) is required to be designed in

the digital peak detection technique. The detailed design of the ADC ASIC will be decribed in the following sections.

Fig. 1. Architecture of the PMT readout electronics.

#### 3 ADC architecture

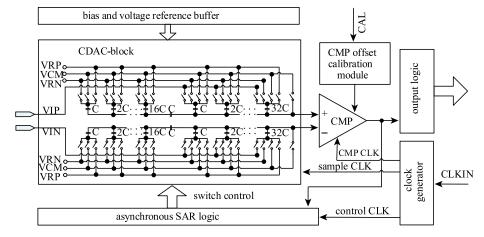

The overall architecture of the implemented 12-bit ADC is depicted in Fig. 2. The ADC mainly consists of a Capacitive Digital to Analog Converter (CDAC), a dynamic comparator, and an asynchronous SAR control logic. A fully differential solution is used to minimize the common mode interference caused by charge injection, digital cross-talk and other disturbances and suppress the even harmonics. The CDAC is responsible for sampling and charge redistribution. For sampling, the bootstrapped switches are employed while CMOS switches are used for charge redistribution. A high-speed and low-noise comparator performs the digitization of the CDAC's voltage differences. Both CDAC and dynamic comparator consume no static power. To further lower the power consumption of the clock tree and increase conversion speed, asynchronous control logic is implemented based on a dynamic latch structure. Besides, the ADC integrates bandgap bias, voltage reference buffer, and clock generator. To save power, the four ADC channels share bias and clock generator, while the reference buffers are provided independently to avoid interfering with each other when large currents are drawn from them at the same time. The implementation of main ADC blocks is described in the following sections.

# 4 Circuit implementation

#### 4.1 Design considerations

The ADC performance is restricted by the trade-off between accuracy, power and speed. To achieve a 12-bit resolution, the noise from comparator and CDAC should be less than 0.5 mV (1 LSB). However, suppressing the noise of the comparator and CDAC excessively will cause higher power consumption. To achieve 40 MSPS, we allocate about 20% of the period time (5 ns) for sampling while the rest (20 ns) is for conversion. This time allocation aims to minimize the total power consumption of sampling and conversion.

Fig. 2. Architecture of the designed ADC ASIC.

## 4.2 Bootstrapped switch

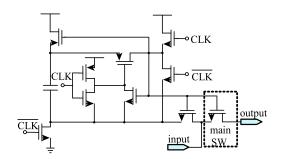

A bootstrapped switch [24–25], as shown in Fig. 3, is employed to reduce the variation of on-resistance and improve the switch linearity. In the sampling phase, the bootstrapped switch and CDAC perform the Sample/Hold (S/H) function. The differential solution and bottom-plate sampling are adopted to minimize non-idealities (the clock feedthrough and charge injection), which can improve the dynamic performance of ADC. The on-resistance of the bootstrapped switch is optimized to be about 50  $\Omega$  when the tracking time is set to 5 ns. As shown in Fig. 4, the ENOB of the S/H module is better than 12.5 bits with 1.8 pF input capacitance.

Fig. 3. Schematic of the bootstrapped switch.

#### 4.3 Capacitive DAC

To further lower the power consumption, the CDAC incorporates a split capacitor structure and  $V_{\rm CM}$ -based switching scheme [26–27]. Compared with the conventional switching scheme, the  $V_{\rm CM}$ -based method saves about 87% power. Besides, the 12-bit resolution can be achieved by employing 11-bit CDAC, which decreases the mismatch requirement and saves chip area. As shown in Fig. 2, in each CDAC array there are M=6 capacitors on the Most Significant Bits (MSB) side and L=5 capacitors on the Least Significant Bits (LSB) side. Metal-Insulator-Metal (MIM) capacitors are used

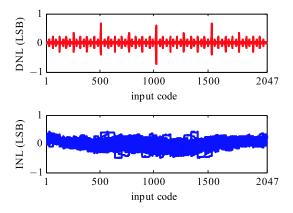

to implement CDAC due to their good matching performance. As shown in Fig. 5, the Monte Carlo simulation of the CDAC indicates the DNL and INL are less than 1 LSB when the unit capacitance is about 28 fF. The total capacitance of CDAC MSB side is about 1.8 pF, which makes the thermal noise much smaller than the quantization noise of 12-bit resolution.

Fig. 4. ENOB simulation of results of S/H module.

Fig. 5. Monte Carlo simulation of DAC in 50 runs.

Each bit of CDAC settling accuracy is determined by its time constant constituted by on-resistance of the CMOS switch and capacitance of the CDAC capacitor. The size ratio of the CMOS switch in each CDAC bit is set according to the capacitance ratio to make each bit have the same time constant. The settling time of 0.5 LSB accuracy for 500 mV step pulse is optimized to less than 600 ps.

#### 4.4 Dynamic comparator

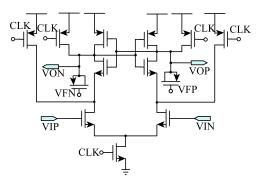

The designed dynamic comparator [28–29] is presented in Fig. 6. To achieve better speed performance in 180 nm CMOS technology, a structure without a preamplifier is adopted. The operating speed of the comparator can be up to 1 GHz for 1 LSB imbalance.

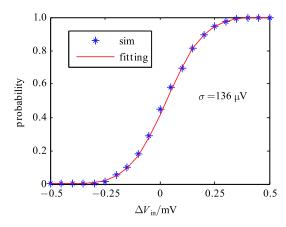

Figure 7 shows the simulation results of the comparator noise obtained with Spectre transient noise simulation. Fitting the simulation results to a Gaussian cumulative distribution, we find that the RMS equivalent input noise is about 136  $\mu V$  (<0.3 LSB).

Fig. 6. Schematic of dynamic comparator.

Fig. 7. Noise simulation of dynamic comparator.

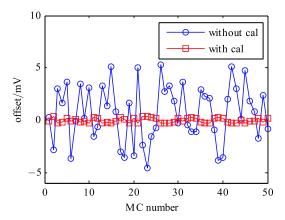

Small areas of input transistor gates are chosen to obtain a high speed. However, smaller sizes of input transistors will cause larger mismatches and consequently, a large input referred offset. We use on-chip offset calibration [30] to compensate for this defect and allow a low power implementation of the comparator. Figure 8

presents the Monte Carlo simulation results of offset calibration. Before calibration, the RMS value of offset is 2.7 mV while the RMS value is about 200  $\mu$ V (< 0.5 LSB) after calibration.

Fig. 8. Monte Carlo simulation of offset calibration.

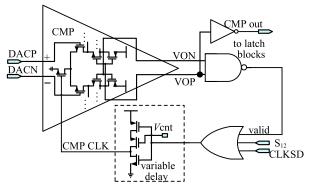

# 4.5 Asynchronous SAR logic

Compared with synchronous SAR control logic, the asynchronous implementation [31] is much more efficient to achieve higher sampling rate and lower power consumption. For high-speed asynchronous logic, the conversion phase needs an internal high-frequency multiphase clock to trigger the comparator. A gate-controlled ring oscillator (GCRO) [32], as shown in Fig. 9, is adopted to generate the multi-phase clock. The signal "CLKSD" shown in Fig. 9 starts the conversion while the "S<sub>12</sub>" stops the conversion. The voltage controlled variable delay is employed to adapt the comparator clock variation due to the process corner.

Fig. 9. Schematic of multi-phase clock generator. "CLKSD" is a delay signal of sample clock and "S<sub>12</sub>" is the flag signal indicating the end of conversion.

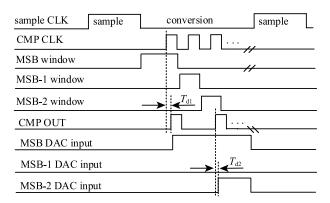

The conversion phase contains twelve periods of comparator clock, each of which includes DAC settling time, comparator decision time and SAR logic delay. Dynamic logic based on the "window-opening" scheme [33], which

can reduce the delay of the SAR logic, is incorporated to minimize the conversion time. The SAR logic adopts twelve latch blocks to generate CDAC digital input signal and 12-bit ADC output code. During bit cycling, each decision result of the dynamic comparator is locked by one latch block when it is enabled by the corresponding "window" signal, which is generated by the window generator. The timing diagram of SAR logic is presented in Fig. 10. In each period of sample clock ("Sample CLK"), the ADC operates in two phases: sample phase and conversion phase. The ratio of the two phases is adjusted by a Delay-Locked Loop (DLL). In the conversion phase, the sampled voltage is quantized under the control of SAR logic. When the "window" signal is valid, the corresponding latch block locks the decision result ("CMP OUT") of comparator and then the SAR logic passes it to the CDAC to change its output value. The above cycle is repeated twelve times in each conversion phase and then the SAR logic resets the latch blocks for next conversion. Each bit delay (" $T_{d2}$ " in Fig. 9) of the SAR logic is about 80 ps, which is much less than conventional DFF-based SAR logic.

Fig. 10. Timing diagram of asynchronous SAR logic. " $T_{\rm d1}$ " is the delay of comparator decision and the " $T_{\rm d2}$ " is the latch delay of SAR logic.

## 5 Simulation results

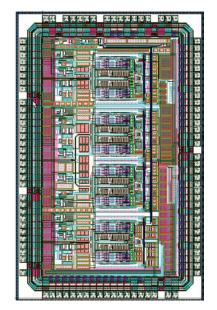

The prototype ADC was designed in Global Foundry 1P6M 180 nm CMOS technology. Figure 11 shows the layout of the chip. It occupies a total area of 3 mm×2 mm and contains four ADC channels. A full-scale input range of 2  $V_{\rm pp}$  is achieved when the power supply is 1.8 V and common mode voltage  $V_{\rm CM}$  is 1 V. Simulations were conducted to estimate the ADC performance and the results show as follows.

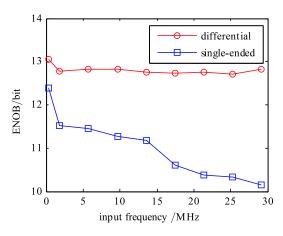

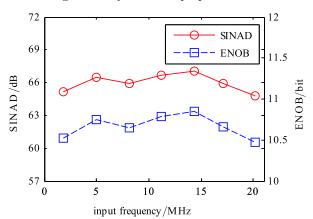

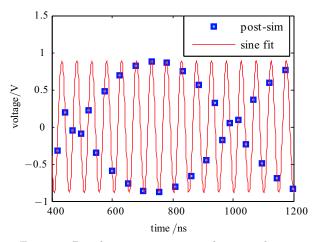

We input a differential sinusoidal signal to the ADC in the Spectre transient noise simulation environment. Figure 12 plots the signal-to-noise-and-distortion ratio (SINAD) and ENOB values versus the input frequency while operating at 40 MSPS. The sine wave curve fit

method [34] is adopted to reduce simulation time by using fewer samples than that of Fast Fourier Transform (FFT). A least-squared-error sine wave is fit to the output data of the ADC, and the resulting error of the two curves represents the power of noise and distortion. The signal power can be calculated by using the amplitude of the fit sinusoid.

Fig. 11. Layout of the proposed ADC.

Fig. 12. Simulation of SINAD and ENOB versus input frequency.

Chip performance is summarized in Table 1. The ADC achieves 10.47-bit ENOB and the core part consumes 6.6 mW, which leads to a Figure-of-Merit (FOM) [35] of 116 fJ/conv-step.

We extract the parasitics from the layout and conduct the post-layout simulation. The transient simulated waveform is shown in Fig. 13. The post-layout simulated ENOB for Nyquist input frequency signal is 9.69 bits, which is 0.78 bit worse than that of pre-simulation. Chip verification will be done when the wafers come back.

Table 1. Performance summary.

| parameter              | value                        |  |

|------------------------|------------------------------|--|

| technology             | 180 nm CMOS                  |  |

| power supply           | 1.8 V                        |  |

| sampling rate          | 40 MSPS                      |  |

| resolution             | 12 bit                       |  |

| full scale input       | $2~\mathrm{V_{pp}}$          |  |

| ENOB                   | 10.47  bits  @20.2  MHz      |  |

| SINAD                  | $64.8~\mathrm{dB}$ @20.2 MHz |  |

| core power consumption | $6.6~\mathrm{mW}$            |  |

| FOM                    | 116  fJ/conv-step            |  |

|                        |                              |  |

Fig. 13. Post-layout transient simulation with sine input waveform.

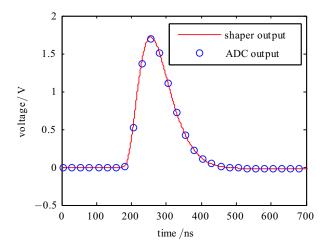

We also simulated the ADC with the output signal of the front-end ASIC [20], which has a fast peaking time of 80 ns. As shown in Fig. 13, the samples of the ADC retain the information of the shaped signal well. The peak value of 1 P.E. shaped signal is 17.6

mV [20] and the equivalent input noise of the ADC is  $0.5~\mathrm{mV}$ , which means that the charge resolution contributed by this ADC is better than 5% for 1 P.E. input signal.

Fig. 14. Simulation with the shaped signal.

#### 6 Conclusions

A 12-bit 40 MSPS asynchronous SAR ADC ASIC prototype in 180 nm CMOS technology is presented. Details regarding the key parts such as CDAC, dynamic comparator and asynchronous SAR logic are discussed. We have finished the design of the ADC which is now in fabrication, and conducted simulations to estimate its performance. The simulation results indicate that this ADC achieves 10.47-bit ENOB while its core power consumption per channel is 6.6 mW. The charge resolution contributed by this ADC is better than 5%@ 1 P.E., which is good enough for the readout requirement of LHAASO WCDA.

# References

- Z. Cao (LHAASO Collaboration), Chin. Phys. C (HEP & NP), 34(2): 249–252 (2010)

- 2 Q. An, Y. X. Bai, X. J. Bi et al Nucl. Instrum. Methods A, 724: 12–19 (2013)

- 3 Z. Cao, Nucl. Insturm. Methods. A, **742**: 95–98 (2014)

- 4 M. Bouchel, F. Dulucq, J. Fleury et al. SPIROC (SiPM Integrated Read-out Chip): Dedicated very front-end electronics for an ILC prototype hadronic calorimeter with SiPM read-out., in *Proc. of IEEE Conf. on Nucl. Sci. Sym. Honolulu* (2007), p. 1857–1860

- 5 S. C. Di Lorenzo, J. E. Campagne, F. Dulucq et al. PARISROC, a photomultiplier array integrated read out chip, in *Proc. of IEEE Conf. on Nucl. Sci. Sym. Orlando* (2009), p. 1074–1081

- 6 S. Blin, P. Barrillon, C. de La Taille. MAROC, a generic photomultiplier readout chip, in *Proc. of IEEE Conf. on Nucl. Sci. Sym. Knoxville*, TN (2010), p. 1690–1693

- 7 G. De Geronimo J. Fried, L. Shaorui et al, IEEE Trans. Nucl. Sci., 60 (3): 2314–2321 (2013)

- A. Aspell, M. De Gaspari, H. Franca et al, IEEE Trans. Nucl. Sci., 60 (2): 1289–1295 (2013)

- E. Atkin, V. Ivanov, P. Ivanov et al, J. Instrum., 10: C04006 (2015)

- 10 M. J. Lee, D. N. Brown, J. K. Chang et al J. Instrum., 10: P06007 (2015)

- H. Abramowicz, FCAL Collaboration. J. Instrum., 10: P05009 (2015)

- E. Delagnes, P. Abbon, Y. Bedfer et al, IEEE Trans. Nucl. Sci., 47 (4): 14471453 (2000)

- H. Nishino, K. Awai, Y. Hayato et al, Nucl. Instrum. Methods A, 610: 710717 (2009)

- 14 A. Comerma, D. Gascon, L. Freixas et al. FlexToT-Current mode ASIC for readout of common cathode SiPM arrays, in Proc. of IEEE Conf. on Nucl. Sci. Sym. Seoul (2013), p. 1–2

- S. Ferry, F. Guilloux, S. Anvar et al, Nucl. Instrum. Methods A, 725: 175178 (2013)

- 16 E. Delagnes, Y. Degerli, P. Goret et al, Nucl. Instrum. Methods A, 567: 2126 (2006)

- 17 E. Oberla, J. F Genat, H. Grabas et al, Nucl. Instrum. Methods A, 735: 452461 (2014)

- 18 S. Ritt, Design and performance of the 6 GHz waveform digitizing chip DRS4, in Proc. of IEEE Conf. on Nucl. Sci. Sym. Dresden (2008), p. 1512–1515.

- 19 L. Tibaldo, J. A. Vandenbroucke, A. M. Albert et al. TARGET: toward a solution for the readout electronics of the Cherenkov Telescope Array, in  $Proc.\ of\ 34^{\rm th}\ ICRC\ Hague\ (2015).$

- 20 J. F. Liu, L. Zhao, L. Yu et al, arXiv: 1510. 00778

- M. Firlej, T. Fiutowski, M. Idzik et al, J. Instrum., 10: P11012 (2015)

- 22 M. Zeloufi (The ATLAS Collaboration), A 12bits 40 MSPS SAR ADC with a redundancy algorithm and digital calibration for the ATLAS LAr calorimeter readout, in *Proc. of TWEPP* (Lisboa, 2015)

- 23 J. Kuppambatti, J. Ban, T. Andeen et al, J. Instrum., 8: P09008 (2013)

- 24 M. Dessouky, A. Kaiser. Electron. Lett., 35 (1): 8–10 (1999)

- 25 G. Z. Huang, P. F. Lin, A fast bootstrapped switch for high-speed high-resolution A/D converter, in *Proc. of IEEE APC-CAS* (Kuala Lumpur, 2010), p. 382–385.

- 26 Y. Zhu, C. H Chan, U. F. Chio et al, IEEE J. Solid-ST. Circ.,

- **45** (6): 1111–1121 (2010)

- 27 V. Hariprasath, J. Guerber, S-H. Lee et al, Electron. Lett., 46 (9): 620–621 (2010)

- 28 G. Van der Plas, B. Verbruggen IEEE J. Solid-ST. Circ., 43 (12): 2631–2640 (2008)

- 29 Y. Zhu, C. H. Chan, S. W. Sin et al, IEEE J. Solid-ST. Circ., 47 (11): 2613–2626 (2012)

- 30 C. H. Chan, Y. Zhu, U. F. Chio et al. A voltage-controlled capacitance offset calibration technique for high resolution dynamic comparator, in *Proc. of ISOCC* (Busan, 2009), p. 392– 395

- 31 S.-W. M. Chen R. W. Brodersen. IEEE J. Solid-ST. Circ., 41 (12): 2669–2680 (2006)

- 32 C. Y. Xue, Y. Wang, F. L. Li et al, An 11-bit 200MS/s SAR ADC IP for wireless communication SOC, in *Proc. of ICSICT* (Guilin, 2014), p. 1–3

- 33 L. Yuxiao, S. Lu, L Zhe et al, Journal of Semiconductors, 35 (4): 045009 (2014)

- 34 http://web.mit.edu/klund/www/papers/UNP\_A2Dtest. pdf, retrieved 5<sup>th</sup> January 2016

- R. H. Walden. IEEE J. Sel. Areas Commun., 17 (4): 539–550 (1999)